## Choosing the Best System Architecture for Tradeoffs in your SDR Design

#### Jeffrey Pawlan Pawlan Communications San Jose, CA USA

Jeffrey Pawlan, Pawlan Communications

#### Outline

For every receiver and transmitter specification, there are many possible implementations:

List and Understand the Specifications

What are the Implications of the Specifications on the Design Implementation?

List and Discuss Important Design Tradeoffs

What to Do when Cost is Primary and Performance is Secondary

Jeffrey Pawlan, Pawlan Communications

#### **Outline continued**

What to Do when Power Consumption is Primary. What might be sacrificed?

#### High Performance and High Reliability Systems •Cell base stations

- Military communications

- •Space communications

#### **Outline continued**

# This presentation will be interactive and the attendees will be asked to participate.

The majority of block diagrams will be drawn on the screen during the lecture. This will be done using a tablet and pen and work like a white board in a classroom.

Jeffrey Pawlan, Pawlan Communications

#### Carefully Read and Understand the Technical Specifications

- •Frequency Band(s)

- •Types of Signals and their bandwidths

- •Number of Signals to be Simultaneously Received or Transmitted

- •What is the Dynamic Range Requirement

- Distortion Requirements (both Rx and Tx)

- How much Rejection of Images

- How much Rejection of out-of-band signals

Noise Floor

- •Frequency Stability

## Design Tradeoffs -- an interactive discussion

- •Performance

- Reliability

- Environmental specs

- Power consumption

- •Heat dissipation methods allowed

- •Cost

Availability of all components

Labor required for tuning or alignment

- •Size and weight

- Ease of modifying and upgrades

## What are the Implications of the Specifications on the Design Implementation?

•Start by drawing a conventional analog block diagram that you think would satisfy the specification requirements without considering the design tradeoffs.

•Look at your design tradeoffs on this product

## •Now think about changes you must make as a result of the additional tradeoffs

Jeffrey Pawlan, Pawlan Communications

## Modify your Block Diagram to Include the Design Tradeoffs

#### What can you do if:

- •cost is more important than performance,

- power consumption is the primary concern

- size or shape is the primary

- weight is the primary

- reliability is primary

- performance over a wide temperature range

- adaptations to future standards is primary

#### Audience Participation: other design tradeoffs suggested:

Jeffrey Pawlan, Pawlan Communications

#### What to Do When Cost is Primary and Performance is Secondary

#### **Use inexpensive components. Rules out:**

- most custom RF filters

- circuits that requires alignment

- expensive high performance FPGAs

- PCBs with high performance teflon or ceramic materials

- high density BGA packaged devices that require many layers for layout

precision machined cavities

What to Do when Power Consumption is Primary

•Consider low voltage parts

- •Use high efficiency circuits

- •Reduce the number of stages

- •Do most of the signal processing at baseband or a low frequency IF

#### **Interactive participation**

## What to Do when Power Consumption is Primary Interactive participation

Jeffrey Pawlan, Pawlan Communications

#### **Design Tradeoffs** when Power Consumption is Primary

**Downside: what might be sacrificed?**

Low voltage = small voltage swing

- Limits the dynamic range and increases distortion

- reduces SNR

- increased susceptibility to noise both on board and from outside

#### **Interactive participation**

Jeffrey Pawlan, Pawlan Communications

#### **1.** How are the IF frequencies chosen?

- Bandwidth specification

- Image, Alias, and IMD reduction

- Out-of-band strong signal rejection

- Component cost & availability

- Speed of the A/D converters

## **2.** Mixer choices

- Conventional double balanced mixers

- Subharmonic double balanced mixers

- Monolithic active mixers, single ended

- Monolithic active mixers, quadrature

- All-digital mixers

- Switching mixers

- Mixers in the digital time domain

**3.** How are the A/D converters chosen?

- Required bandwidth

- Dynamic Range ENOB

- Cost & availability

- Power consumption

#### **High Performance and High Reliability**

#### systems include:

#### **Cell base-stations**

#### **Military communications**

#### **Space communications**

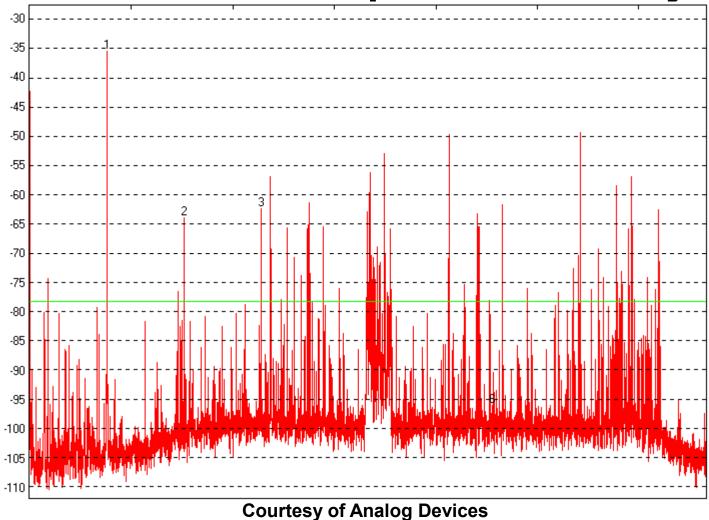

#### **Actual Cell Site Spectrum Survey**

Jeffrey Pawlan, Pawlan Communications

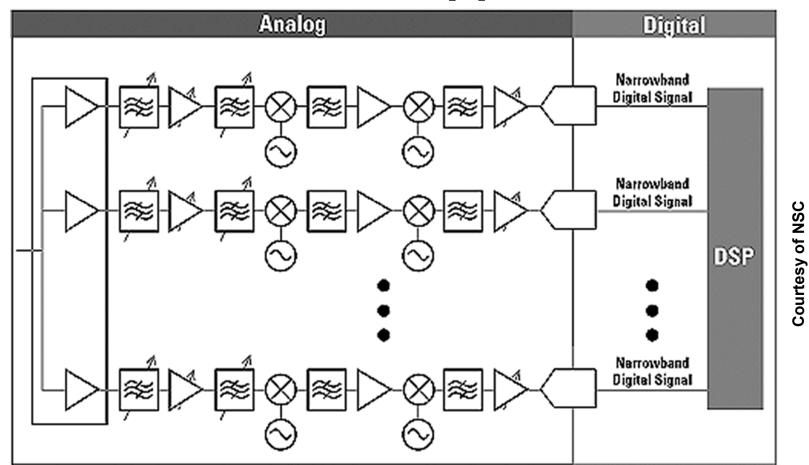

#### Cell Base-station Design Traditional Approach

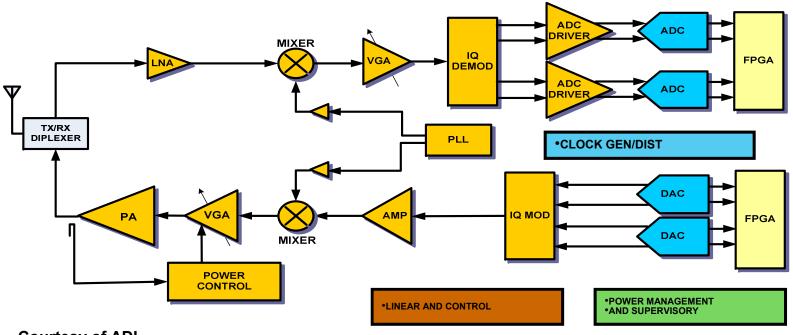

#### Cell Base-station Design Possible SDR Implementation

**Courtesy of ADI**

Jeffrey Pawlan, Pawlan Communications

## Looking at the previous slide

What is the IQ Demod part? Why are there two A/D converters? Advantages of this circuit: Low cost Wide bandwidth Good image rejection **Disadvantages of this circuit:** Moderately high noise figure **Requires diff inputs + stable DC Temperature compensation needed** Image rejection varies with frequency

## Looking at the previous slide

What is the IQ Mod part? Why are there two D/A converters? Advantages of this circuit: Low cost Wide bandwidth Good image rejection **Disadvantages of this circuit:** Moderately high noise figure **Requires diff inputs + stable DC Temperature compensation needed** Image rejection varies with frequency

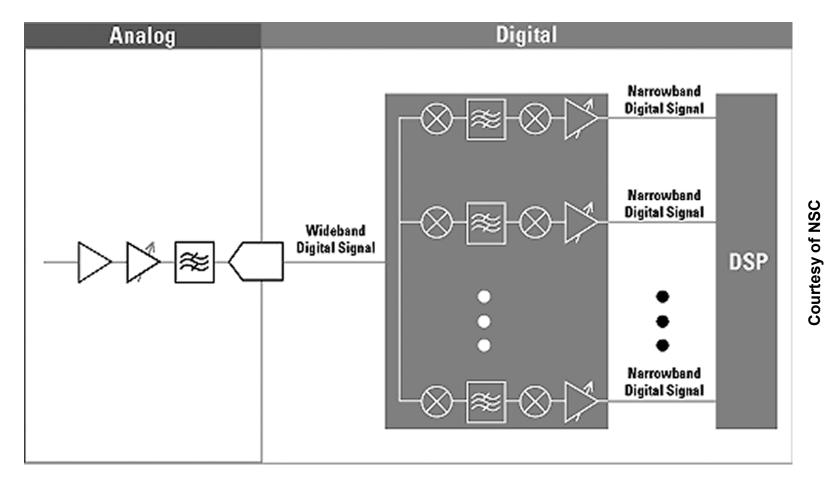

## Cell Base-station Design New SDR Approach

Do as much mixing and signal processing as possible within the FPGA

Quadrature is excellent, making near perfect image rejection

Lock UHF, microwave oscillators to an external reference

**Complete stability over temperature range**

#### Transmit PA can have digital pre-distortion

Jeffrey Pawlan, Pawlan Communications

#### Cell Base-station Design New SDR Approach

Jeffrey Pawlan, Pawlan Communications

## Cell Base-station Design New SDR Approach

Notice that only one A/D converter is needed when the mixer is implemented in the FPGA How does this work?

Notice that the only one RF chain with one A/D converter can now demodulate many independent channels simultaneously Just use a larger FPGA

Jeffrey Pawlan, Pawlan Communications

## Military Communications

The dynamic range requirement depends on the frequency band

High reliability and wide temperature range

#### Power dissipation methods may be limited Often airtight and no fans

**Usually requires approved parts**

#### Interactive participation

## **Space Communications**

#### S-Band near earth: 2.025 – 2.1GHz paired with 2.2GHz – 2.3GHz 3MHz PN coded

X-Band: 7.15GHz paired with 8.4GHz 100MHz wide for near earth 50MHz wide for deep space

Ka-Band: 32GHz paired with 34GHz 100MHz wide

Jeffrey Pawlan, Pawlan Communications

## **Space Communications**

These bands are generally devoid of interference and strong signals

The modulation is constant envelope

Therefore only needs low dynamic range

Working backwards in the chain: •Pick the A/D converters first •Use either passive or active mixers that meet the reliability requirements •Space = low power

#### Interactive discussion of S-Band Receiver Design

•Front End •1<sup>st</sup> IF •2<sup>nd</sup> IF •3<sup>rd</sup> IF •A/D

Jeffrey Pawlan, Pawlan Communications

#### Interactive participation block diagrams

Jeffrey Pawlan, Pawlan Communications

## **Space Communications**

#### **Concentrate on**

- Low phase noise oscillators

- Temperature and vibration stability

- Radiation hardness for space

#### Interactive participation

#### Within the limitations of cost, power consumption, and reliability put as much of the signal processing chain within a FPGA as you can.

Jeffrey Pawlan, Pawlan Communications

Advantages of putting the mixer, LO, filters, and demodulators in a FPGA

•Dynamic range and also phase noise are limited only by the number of cells used in the FPGA

•Everything implemented in the FPGA cannot drift with temperature or aging

## •Improvements or changing standards can be quickly loaded

Jeffrey Pawlan, Pawlan Communications

## What can you do in the software?

- The outputs from the FPGA are usually further processed by software running under an operating system.

- Operator control of parameters

- Display of the signals

- Narrowband filtering

- Noise reduction

- Demodulation

#### **Remote Processing**

# You may want to remotely control a receiver or station

#### The signal processing functions may be split between the station site and the control site

# Ethernet or a radio link may connect the two sites

Jeffrey Pawlan, Pawlan Communications

#### **Radio Demonstration**

## Show the overall result when some of the processing is done in the FPGA and some is done in software running on a computer

Jeffrey Pawlan, Pawlan Communications

## **Contact Information Jeffrey Pawlan Pawlan Communications** 14908 Sandy Ln. San Jose, CA 95124 1 (408) 371-0256 pawlan@ieee.org www.pawlan.com